芯片最小能做到多少纳米,达到极限后,该如何突破瓶颈?

芯片最小能做到多少纳米,达到极限后,该如何突破瓶颈?

-

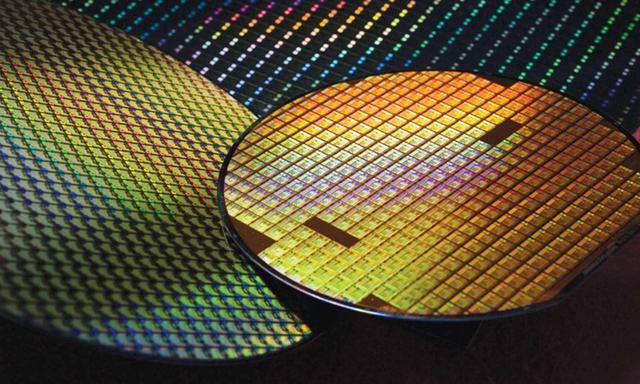

目前,手机处理器是7nm,台积电即将量产5nm芯片,未来还有3nm、2nm,甚至1nm。根据台积电研发负责人在谈论半导体工艺极限问题时,认为到了2050年,晶体管可以达到氢原子尺度,即0.1nm,那么半导体工艺的“物理极限”是什么呢?

制程工艺

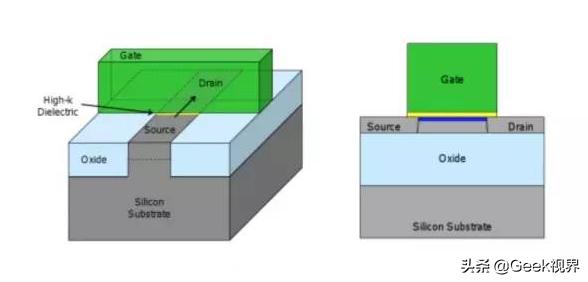

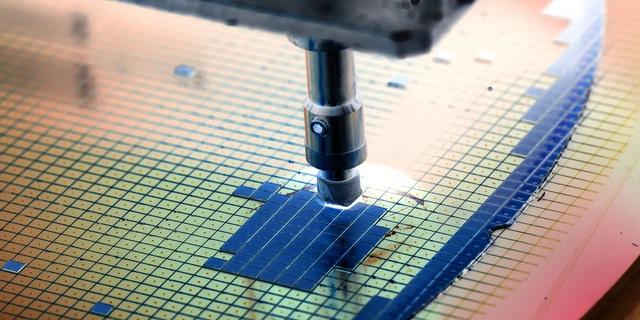

首先,我们了解一下芯片的制程工艺。华为的麒麟990处理器,指甲壳大小,集成了上百亿的晶体管,单个晶体管的结构如下图所示▼。

在晶体管中,电流是从源极(Source)流向漏极(Drain),而栅极(Gate)相当于闸门,主要负责两端源极和漏极的通断。通代表1,断代表0,这样就实现了计算机世界的0、1运算。栅极的宽度,也称为删长,就是所说的xx nm制程工艺。

通常来说,制程工艺越小,晶体管删长越小,电流通过时的损耗越少,表现出来就是手机常见的发热和功耗。同时,单位面积的芯片可以容纳更多的晶体管。因此,晶圆代工厂不断的升级技术,力求将栅极宽度做的越来越窄。然而,工艺的提升会受到光刻机技术、芯片“物理极限”等多方面因素的限制。

如何突破技术限制?

①更换材料。目前,芯片采用的是硅基半导体结构,根据台积电的规划,今年实现5nm工艺,2022年实现3nm工艺,2024年实现2nm工艺,正在逼近1nm。2017年,IBM科研团队在实验室环境下,使用碳纳米材料,制造出了1nm的晶体管,1nm工艺后的芯片,可能采用纳米片、碳纳米管等新材料。

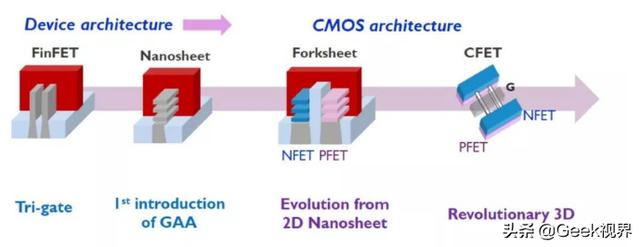

②结构的升级。目前,芯片制造采用了FinFET结构,随着工艺的提升,FinFET技术探底,新的结构将会诞生。2nm技术节点将会爱用Forsheet结构,1nm节点是采用CFET结构。

不过,芯片制造总是有“物理极限”的,将会产生“量子效应”,PN结不能形成之前的工作状态,无法表现出0和1这种状态,取代数字电路的技术可能就是“量子计算”了。

如果觉得对你有帮助,可以多多点赞哦,也可以随手点个关注哦,谢谢。

2020-05-27 22:12:18 -

芯片最小能做到多小?目前的硅基物质材料芯片,已经做到5nm大小。台积电公司预计2020年底2021年初可以量产5nm芯片。而三星电子预计2022~2023年可以量产3nm硅基芯片。根据相应的物理定律,硅基芯片最小可以做到3nm。达到3nm之后的硅基芯片该如何突破?答案可能在新材料上。

3nm硅基芯片受限与晶体管热效应的因素,在小的话可能就无法容纳更多的晶体管数量,而无法提高运算速度。

现在的新材料中下一代的晶体管可能会从“石墨烯,碳纳米管,锗,砷化镓,氮化镓,砷化铟镓,锑化镓”这七种材料中选择出具有发热小,电子迁移率高,承载电流大性能的材料出来。

目前已经在“碳纳米管,砷化铟镓,氮化镓”这三种材料用于制造晶体管了,并且取得了一些进展。

1.

碳纳米管。2019年美国一个科研团队就在碳基芯片上集成了1.4万个碳纳米管晶体管,但是相比于如今硅基芯片上数十亿个晶体管的确是有天壤之别。所以说,碳纳米管制作晶体管还有很长的一段路要走。我国已经研制出了3纳米的碳纳米管,正在向0.5纳米的碳纳米管进发。

2.

砷化铟镓,在2012年,受早期关于纳米线晶体管和超晶格结构研究的启发,科研人员就用砷化铟镓构造了三层纳米片器件晶体管,最终实验结果好于预期。

3.

氮化镓。对于这一名称我们比较陌生,不过相信对有源相控阵雷达比较了解的读者就比较清楚了,使用氮化镓T/R组件的有源相控阵雷达的性能,要比使用砷化镓T/R组件的有源相控阵雷达性能强的多,更比使用硅晶体管作T/R组件的有源相控阵雷达性能更强的多。三种材料之间的差距基本上就相当于SPY-6和346B和346雷达之间的差距所以说,使用氮化镓技术后,芯片的性能可以得到较大的提升。目前来看,氮化镓已经被用于5G技术了。

至于硅基芯片是否可以突破3nm的限制,也许会有惊喜等着我们。但以目前的技术看来很难突破。

不过,只要是芯片的运行规律还是通过晶体管实现的话,那么光刻机还是必不可少的。原因是需要将设计好的电路图复刻到芯片上。也就是说,芯片实现其功能的基本物理原量没有变化。光刻机,蚀刻机还是少不了的。在使用光刻机的前提下,国内技术也只能达到追平国际先进技术,等芯片发展到极限时,就没有进一步发展的空间了。

2020-05-27 13:01:38 -

答案也许在大脑!大脑电路仿生也许能开辟另一种思路!

2020-05-27 07:54:21 -

从目前半导体行业发展的趋势来看,芯片发展的极限在2-3nm左右,目前全球领先的芯片代工企业是台积电,芯片制程工艺为5nm。在芯片制程发展到瓶颈以后,最有可能的发展趋势是将硅元素替换成其它元素用以发展。

芯片纳米制程工艺

芯片,作为全球半导体行业最重要的载体,芯片的制造包含以下几个方面:芯片的设计、芯片的制造以及后期的封装测试。而在这三大步骤之中,芯片的制造是最关键的一步,也是最有科技含量的一步。目前全球范围芯片的设计、原材料提供、代工以及后期的封装测试已经形成了一条完整的产业链,各企业之间的分工与合作也不断加深,其中代工晶圆制造的企业包括台积电、英特尔以及三星,在这三者之中又以台积电的技术最为先进,目前台积电的芯片制程工艺已经来到了5nm的水准,而其它代工企业还在7nm甚至是14nm处徘徊。

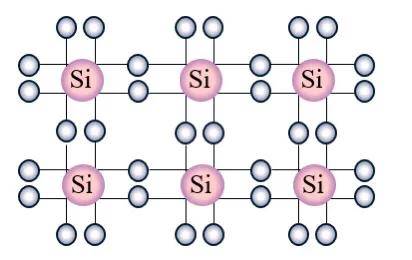

未来芯片的制程工艺会越来越小,比如下一代的制程工艺会在3nm甚至是2nm左右,但是基于硅元素的物理特性,硅原子的半径大小在0.11nm左右,而当到了制程工艺为2nm的时候,一条线上可供操作的硅原子仅仅只有10个左右,对于机器的精密型可想而知要求会有多高,再加上由于在这极限条件下会出现不可预知的比如量子效应、轨道电子相互作用等引起的效应,对于芯片的成品率的影响也是非常大的,因此芯片制程工艺在2-3nm时将达到物理极限,就算是再精密的仪器也不可能继续进行下去。

在达到芯片的物理极限后,最有可能突破的就是通过寻找可替代硅元素的材料,将原有硅元素的特性进行无限放大,而这也将成为未来半导体行业发展的趋势!

2020-05-26 21:00:09 -

目前在攻5纳米。

2020-05-27 08:50:53 -

按理论来说,芯片的最小制程为0.5纳米,因为硅原子的直径为0.22纳米,算上两者之间的距离也就是0.5纳米。但是严格按照摩尔定律的话,那么芯片的最小制程就是3纳米,一旦小于3纳米,就会发生量子遂穿效应,导致芯片的稳定性受到影响。

现在最先进的制程工艺也就是7纳米,明年和后年,台积电和三星将量产采用5纳米和3纳米制程工艺的芯片。如果说到2022年时,3纳米制程的芯片被制造出来,那么接下来传统采用硅基晶体管的芯片也将走到尽头。至于如何破局也只有三个办法:第一:开发替代硅基晶体管的新材料;第二,大力发展新型计算机;第三,试着打破摩尔定律,继续采用硅基晶体管,进一步发掘其潜力。目前来看,第一,第二种办法科学家们正在尝试,并且取得了些许进展。至于是否敢于突破摩尔定律的限制,还得看具体的实验研究。

事实上,现在的手机,电脑在日常使用时性能已经过剩了,也就是说,芯片基于7纳米制程的工艺基本上已经够用了。毕竟芯片的制程优势,并不能让使用者很明显的感受的到,也就是说,在日常的使用中,手机安装10纳米制程工艺的芯片和7纳米制程工艺的芯片展现出来的性能,使用者并不能明显的感觉到两者之间的差异。但是,人类对最新科技的不懈追求是无止境的,也只有这样,才能促进科技和技术的不断发展,使人类文明越来越好,越来越先进。

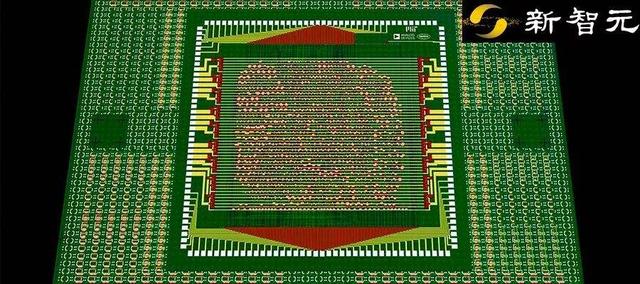

如果当芯片制程工艺达到3纳米后,也就只有上文所列出的三个办法,去进一步促进芯片工艺的进展了。现在来看,量子计算机的发展有了较大的进步,国外和国内对于量子计算机的研究都持续了较长的时间,谷歌公司研发的Sycamore量子计算机是由53个量子组成的,而国内研发的量子计算机是由10个量子组成。可以说,在量子计算机的研究上,已经取得了不小的进展,但是距离实用化,还有很长的路要走。要知道量子计算机产生的热量是非常大的,也需要无数的电线,导致其体积小不下来,根本无法和当今的笔记本相比。想要量子计算机得到发展,就必须解决散热问题,和体积小型化问题。

而采用新材料取代现有的硅基晶体管和硅基芯片也在研发之中,如,碳纳米管晶体管,氮化镓,砷化铟镓等等。对于碳纳米管来说,国内和国外没有多大的差距,基本上处于同一层次。但是其他材料国外也做过相关的实验,至于国内是否做过也无法得知。总之,开发替代硅晶体管的新材料势在必行的,这还需要科学家进一步的进行研究。

最后就是摩尔定律了,在摩尔定律的限制下,芯片的制程工艺为3纳米。但是能否做出小于3纳米的芯片并让其稳定的运行,还需要展开相关的实验。

2020-05-28 18:16:12 -

我们现在使用的芯片都是基于半导体材料硅制作而成即硅基芯片。

硅基芯片

硅原子大小半径为110皮米,也就是0.11纳米,直径0.22nm。虽然3D晶体管的出现已经让芯片不再全部依赖制程大小,而制程工艺的提升,也意味着会决定3D晶体管横面积大小,不过,在不破坏硅原子本身的前提下,芯片制造目前还是有理论极限的,在0.5nm左右,之所以不是0.2nm,是因为本身硅原子之间也要保持一定的距离。而从实际角度上看,我们现在能做到的是量产5nm,所以0.5nm这个理论极限在目前的科学技术上看,几乎是不可能的。

就目前来看台积电、三星都相继进入了5nm芯片量产和3nm芯片的研发,台积电更是率先进入了2nm芯片技术的研发。据台积电披露,5nm和3nm芯片都是过度,2nm芯片才是台积电终极目标,而2nm芯片一旦实现量产,也就意味着芯片已经达到了其物理极限,没有后续发展的空间了。

碳基芯片

目前在有部分公司已经把目光转向了碳基芯片的研制工作,碳基芯片就是微电子和光电子结合的芯片,被认为是未来的芯片技术。

2017年的《自然·通讯》上刊登了完全用碳制成运算元件的设计方案,其可以被制造的更小,且性能更好,从而取代硅晶体管。这样全新的晶体材料可以让新计算系统的通讯速度提升1万倍,时钟频率有望达到每秒一万亿次,比当前主流计算机快1000倍。另外,新原件能被制造得比硅基晶体管小得多。

2020-05-26 16:43:25 -

几年前极限是6,7nm吧,用传统源极漏极栅极结构,随着沟道的变窄,电子的导通关闭越来越难控制,后来一个科学家,美国的吧,提出了一种立体结构,虽然沟道变窄了,但是立体结构对电子控制能力加强了,然后极限推进到了2,3nm,现在5nm投产了吧 3,4nm在建厂,估计怎么也得5年到下一个极限。2,3nm极限到来时估计就该换材料了。

2020-05-26 22:58:47 -

在头条问连科学家都还在研究的问题,重点科学家都还没有谱,问问题也看看场地

2020-05-27 08:36:58 -

到时候肯定有新的材料技术代替旧的,就像是在以前硬盘在某个时段大家都觉得生产工艺突破不了2g的容量,后来的容量按T算

2020-05-27 09:04:24 -

我要知道芯片达到了极限能如何突破瓶颈,那我现在就是全中国最牛的人了。你拿这个问题问我,可真的是太看得起我了。

2020-05-27 07:25:17 -

目前是3至5纳米,再小就看科学研究的的突破或新材料的出现了。

2020-05-26 20:35:03 -

新的替代产品产出!

2020-05-27 08:22:52 -

现在的硅基芯片上限是1.5纳米,就算有1纳米也是千分之一的成功率。中科院最近研发成功的碳基晶元能做到0.1nm,而且传输速度是硅基芯片的大概100倍,碳的稳定性是地球上最高的,还不怕水。但是怕高温(3000度)

2020-11-24 22:45:20 -

我感觉电子工业发展的极限还没到来,我觉得芯片元件最小尺寸可以做到2pm级别,那样的话,光刻机还有一百年的发展历程,我国有机会攻上去,现在光刻机激光波长在100nm级别,说明还可以做到更短,比如1nm波长,那就是不可见光了,能用就行,那时候,芯片体积缩小了一千倍,是不是能力相当于现在的一千个手机芯片那么强?那样的话,每一个手机就是一个云计算节点,包含当前一千台计算节点能力,可以满足部署一个智慧城市的计算能力需求,再加上端到端6G互联通信技术,每秒传输数据能力在1PB/秒,那时候,计算和通信就再也不是问题,所有的计算和应用,都是眨眼完成的速度,你能知道,你想知道的一切!

2020-05-27 08:08:31